基于量子阱二极管的闪存装置的制作方法

1.本发明涉及无线光通信技术领域,尤其涉及一种基于量子阱二极管的闪存装置。

背景技术:

2.可见光通信技术是通过控制led(发光二极管)的亮灭来实现信息的传输。当前可见光通信装置的传输速率可达到gb/s级别。传统的无线电信号传输设备存在很多局限性,例如价格昂贵、但效率不高,比如手机,在全球通过建立数百万个基站来增强手机传输信号,但是大部分能量却消耗在设备冷却上,能量有效利用效率只有5%。相比之下,可见光通信技术本质上是通过光信号来实现信息的传输,所需的传输设备只有led,且不占用现有的频带资源,因而也就不会与现有的频段设备之间产生相互干扰,从而使得可见光通信方式具有良好的通信质量和保密性,且更加的绿色环保。可见光通信作为射频通信的备用方案越来越受到高校、研究机构的重视。目前,可见光通信装置采用的是led-pds(发光二极管-光电二极管),这就使得可见光通信装置的体积大、成本高。另外,当前的闪存装置仅用于信息的存储,功能较为单一。而且,现有的闪存装置的性能有待进一步提高。

3.因此,如何改善闪存装置的性能,并扩大闪存装置的应用领域,是当前亟待解决的技术问题。

技术实现要素:

4.本发明提供一种基于量子阱二极管的闪存装置,用以改善闪存装置的性能,并扩大闪存装置的应用领域。

5.为了解决上述问题,本发明提供了一种基于量子阱二极管的闪存装置,包括上位机单元和移动单元;其中,

6.所述上位机单元包括主机、与所述主机电连接的第一处理器、与所述第一处理器电连接的第一模式选择电路、与所述第一模式选择电路电连接的第一控制电路、以及与所述第一控制电路电连接的第一量子阱二极管芯片,所述第一控制电路包括第一驱动电路和第一接收电路,所述第一模式选择电路用于根据所述第一处理器的第一选通信号控制所述第一控制电路中的所述第一驱动电路导通或者所述第一接收电路导通,所述第一量子阱二极管芯片包括多个第一量子阱二极管,所述第一驱动电路用于控制所述第一量子阱二极管芯片向所述移动单元发射携带有第一信息的第一光信号;所述第一量子阱二极管芯片还用于接收来自于所述移动单元且携带有第二信息的第二光信号,并传输至所述第一接收电路进行处理;

7.所述移动单元包括存储器、与所述存储器电连接的第二处理器、与所述第二处理器电连接的第二模式选择电路、与所述第二模式选择电路电连接的第二控制电路、以及与所述第二控制电路电连接的第二量子阱二极管芯片,所述第二控制电路包括第二驱动电路和第二接收电路,所述第二模式选择电路用于根据所述第二处理器的第二选通信号控制所述第二控制电路中的所述第二驱动电路导通或者所述第二接收电路导通,所述第二量子阱

二极管芯片包括多个第二量子阱二极管,所述第二驱动电路用于控制所述第二量子阱二极管芯片向所述上位机单元发送所述第二光信号;所述第二量子阱二极管芯片还用于接收所述第一光信号。

8.可选的,所述主机包括第一usb接口,所述第一处理器通过所述第一usb接口与所述主机电连接。

9.可选的,所述上位机单元还包括与所述第一处理器电连接的第一外围电路,所述第一外围电路包括:第一晶振电路、第一复位电路和第一烧写电路,所述第一晶振电路用于产生所述第一处理器的工作频率;所述第一复位电路用于对所述第一处理器进行硬件复位;所述第一烧写电路用于对所述第一处理器进行程序烧录;

10.所述移动单元还包括与所述第二处理器电连接的第二外围电路,所述第二外围电路包括:第二晶振电路、第二复位电路和第二烧写电路,所述第二晶振电路用于产生所述第二处理器的工作频率;所述第二复位电路用于对所述第二处理器进行硬件复位;所述第二烧写电路用于对所述第二处理器进行程序烧录。

11.可选的,所述移动单元还包括:

12.输入结构,用于接收来自外部的触发信号,以触发所述存储器向所述上位机单元发送所述第二光信号。

13.可选的,所述第一驱动电路包括第一发送信号放大电路、以及与所述第一发送信号放大电路电连接的第一偏置电路,所述第一接收电路包括第一跨阻放大电路、与所述第一跨阻放大电路电连接的第一接收信号放大电路、以及与所述第一接收信号放大电路电连接的第一比较器电路;

14.所述第二驱动电路包括第二发送信号放大电路、以及与所述第二发送信号放大电路电连接的第二偏置电路,所述第二接收电路包括第二跨阻放大电路、与所述第二跨阻放大电路电连接的第二接收信号放大电路、以及与所述第二接收信号放大电路电连接的第二比较器电路。

15.可选的,所述第一接收电路包括第一跨阻放大器、与所述第一跨阻放大器电连接的第一电压放大器和与所述第一电压放大器电连接的第一电压比较器;

16.所述第二接收电路包括第二跨阻放大器、与所述第二跨阻放大器电连接的第二电压放大器和与所述第二电压放大器电连接的第二电压比较器。

17.可选的,所述第一接收电路还包括位于所述第一跨阻放大器和所述第一电压放大器之间的第一带通滤波器;

18.所述第二接收电路还包括位于所述第二跨阻放大器和所述第二电压放大器之间的第二带通滤波器。

19.可选的,所述第一模式选择电路包括第一模拟开关,所述第一模拟开关包括第一正电压输入端、第一接地端、第一控制端、第一共同输出端、第一上位机输入端和第二上位机输入端,所述第一上位机输入端电连接所述第一驱动电路,所述第二上位机输入端电连接所述第一接收电路;

20.所述第二模式选择电路包括第二模拟开关,所述第二模拟开关包括第二正电压输入端、第二接地端、第二控制端、第二共同输出端、第一移动单元输入端和第二移动单元输入端,所述第一移动单元输入端电连接所述第二驱动电路,所述第二移动单元输入端电连

接所述第二接收电路。

21.可选的,所述第一模拟开关和所述第二模拟开关均为型号为ts5a23157的模拟开关。

22.可选的,所述第一量子阱二极管芯片包括第一衬底、位于所述第一衬底上的第一量子阱阵列、以及位于所述第一衬底与所述第一量子阱阵列之间的反射镜,所述第一量子阱阵列包括呈阵列排布的多个所述第一量子阱二极管;

23.所述第一量子阱二极管芯片包括第二衬底、以及位于所述第二衬底上的第二量子阱阵列,所述第二量子阱阵列包括呈阵列排布的多个所述第二量子阱二极管,所述第二量子阱二极管为反向偏压二极管。

24.本发明提供的基于量子阱二极管的闪存装置,通过设置上位机单元和移动单元,且所述上位机单元能够向所述移动单元发射第一光信号以及接收来自所述移动单元的第二光信号,所述移动单元能够向所述上位机单元发送所述第二光信号、并接收来自于所述上位机单元的所述第一光信号,使得所述基于量子阱二极管的闪存装置实现了光存储功能、光探测功能、光发射功能的融合集成,从而极大的扩展了所述基于量子阱二极管的闪存装置的功能,扩大了所述基于量子阱二极管的闪存装置的应用领域。同时,可见光通信的方式传输稳定、受外界干扰小、传输速率快等优点,使得所述基于量子阱二极管的闪存装置的性能得到了改善。而且,本发明提供的基于量子阱二极管的闪存装置其核心芯片成本低廉、集成度高、设备体积小,作为一种新型技术路线,进一步扩展了移动存储技术的选择方案,极大提高了u盘类等闪存装置的经济性和科技感。

附图说明

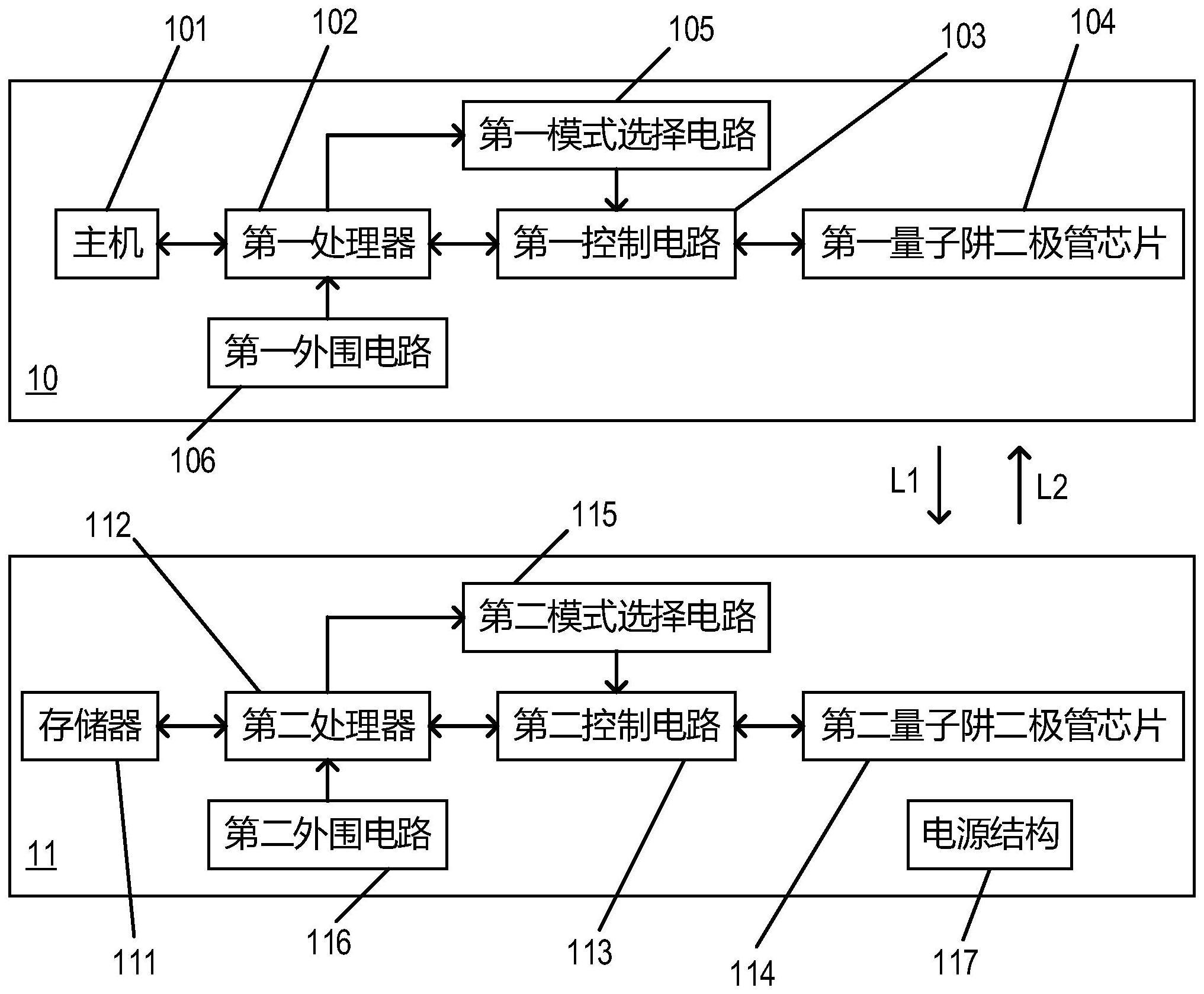

25.附图1是本发明具体实施方式中基于量子阱二极管的闪存装置的结构示意图。

具体实施方式

26.下面结合附图对本发明提供的基于量子阱二极管的闪存装置的具体实施方式做详细说明。

27.本具体实施方式提供了一种基于量子阱二极管的闪存装置,附图1是本发明具体实施方式中基于量子阱二极管的闪存装置的结构示意图。如图1所示,所述基于量子阱二极管的闪存装置,包括上位机单元10和移动单元11;其中,

28.所述上位机单元10包括主机101、与所述主机101电连接的第一处理器102、与所述第一处理器102电连接的第一模式选择电路105、与所述第一模式选择电路105电连接的第一控制电路103、以及与所述第一控制电路103电连接的第一量子阱二极管芯片104,所述第一控制电路103包括第一驱动电路和第一接收电路,所述第一模式选择电路105用于根据所述第一处理器102的第一选通信号控制所述第一控制电路103中的所述第一驱动电路导通或者所述第一接收电路导通,所述第一量子阱二极管芯片104包括多个第一量子阱二极管,所述第一驱动电路用于控制所述第一量子阱二极管芯片104向所述移动单元11发射携带有第一信息的第一光信号l1;所述第一量子阱二极管芯片104还用于接收来自于所述移动单元11且携带有第二信息的第二光信号l2,并传输至所述第一接收电路进行处理;

29.所述移动单元11包括存储器111、与所述存储器111电连接的第二处理器112、与所

述第二处理器112电连接的第二模式选择电路115、与所述第二模式选择电路115电连接的第二控制电路113、以及与所述第二控制电路113电连接的第二量子阱二极管芯片114,所述第二控制电路114包括第二驱动电路和第二接收电路,所述第二模式选择电路115用于根据所述第二处理器112的第二选通信号控制所述第二控制电路中的所述第二驱动电路导通或者所述第二接收电路导通,所述第二量子阱二极管芯片114包括多个第二量子阱二极管,所述第二驱动电路用于控制所述第二量子阱二极管芯片114向所述上位机单元10发送所述第二光信号l2;所述第二量子阱二极管芯片114还用于接收所述第一光信号l1。

30.具体来说,所述上位机单元10与所述移动单元11之间以可见光通信的方式进行信息的传输。所述上位机单元10中的所述主机101一方面用于接收来自外界(即所述基于量子阱二极管的闪存装置的外部)的所述第一信息,并将所述第一信息以光信号(即所述第一光信号l1)的方式传输至所述移动单元11;另一方面,所述上位机单元10还用于接收所述移动单元11以光信号(即所述第二光信号l2)的方式传送来的所述第二信息,并在所述主机101中的显示屏进行显示。所述上位机单元10中的所述主机101的具体类型,本领域技术人员可以根据实际需要进行选择。在一示例中,所述主机101可以是手机、笔记本电脑、台式电脑等智能终端装置。所述移动单元11中的所述存储器11一方面用于接收并存储来自于所述上位机单元10以光信号(即所述第一光信号l1)的形式传送来的所述第一信号;另一方面,所述移动单元11还能够根据来自于外界的触发信号向所述上位机单元10以光信号(即所述第二光信号l2)的形式发送所述第二信号。所述存储器111可以为但不限于sd卡。所述存储器111的存储容量本领域技术人员可以根据实际需要进行选择,例如所述存储器111位存储容量为2g的sd卡。在一示例中,所述存储器111包括esp32芯片。

31.所述第一处理器102用于向所述第一模式选择电路105发送所述第一选通信号,所述第一模式选择电路105根据接收到的所述第一选通信号控制所述第一控制电路103中的所述第一驱动电路导通(即控制所述上位机单元10开启发送模式)或者所述第一接收电路导通(即控制所述上位机单元10开启接收模式)。所述第二处理器112用于向所述第二模式选择电路115发送所述第二选通信号,所述第二模式选择电路115根据接收到的所述第二选通信号控制所述第二控制电路113中的所述第二驱动电路导通(即控制所述移动单元11开启发送模式)或者所述第二接收电路导通(即控制所述移动单元11开启接收模式)。

32.举例来说,所述第一选通信号包括选通所述第一驱动电路的信号和选通所述第一接收电路的信号。所述第一处理器102接收到所述主机101发送的所述第一信号后,控制所述第一模式选择电路105向所述第一控制电路103发送选通所述第一驱动电路的信号,所述第一控制电路103根据接收到的信号控制所述第一驱动电路导通,从而使得所述上位机单元10开启发送模式。当所述第一量子阱二极管芯片104接收到所述第二光信号l2并传输至所述第一控制电路103之后,所述第一控制电路103将接收到所述第二光信号l2的信息反馈至所述第一处理器102,所述第一处理器102控制所述第一模式选择电路105向所述第一控制电路103发送选通所述第一接收电路的信号,所述第一控制电路103根据接收到的信号控制所述第一接收电路导通,从而使得所述上位机单元10开启接收模式。

33.所述第二选通信号包括选通所述第二驱动电路的信号和选通所述第二接收电路的信号。当所述第二处理器112接收到所述存储器111发送的所述第二信号后,控制所述第二模式选择电路115向所述第二控制电路113发送选通所述第二驱动电路的信号,所述第二

控制电路113根据接收到的信号控制所述第二驱动电路导通,从而使得所述移动单元11开启发送模式。当所述第二量子阱二极管芯片114接收到所述第一光信号l1并传输至所述第二控制电路113之后,所述第二控制电路113将接收到所述第一光信号l1的信息反馈至所述第二处理器112,所述第二处理器112控制所述第二模式选择电路115向所述第二控制电路113发送选通所述第二接收电路的信号,所述第二控制电路113根据接收到的信号控制所述第二接收电路导通,从而使得所述移动单元开启接收模式。所述移动单元11实时检测是否接受到来自于外界的触发信号,若是,则通过所述第二模式选择电路115选通所述第二驱动电路(即使得所述移动单元11处于发送模式);若所述移动单元未接收到来自于外界的所述触发信息,则所述第二模式选择电路115保持选通所述第二接收电路的状态(即保持所述移动单元11处于接收模式)。

34.可选的,所述主机101包括第一usb接口,所述第一处理器102通过所述第一usb接口与所述主机101电连接。

35.为了简化所述基于量子阱二极管的闪存装置的制造工艺,且同时减少所述上位机单元10与所述移动单元11之间的信号处理延时差异,可选的,所述第一处理器102的结构与所述第二处理器112的结构相同。所述第一处理器102和所述第二处理器112的功能均包括信号接收、信号发送、调制解调、信号编码、信号采样、信号量化、信号同步、串口通信、端口控制、spi(serial peripheral interface,串行外设接口)协议/ⅱc(inter-integrated circuit,串行通信)协议、数据存储、数据擦除、数据重写、有固定时钟。所述第一处理器102与所述主机101之间的通信方式为串口通信,通信波特率为9600或者115200,也可以根据需要添加校验位;所述第二处理器112与所述存储器111之间的通信方式也为串口通信,通信波特率为9600或者115200,也可以根据需要添加校验位。在一示例中,所述第一处理器102和所述第二处理器112均为单片机或者fpga(field programmable gate array,现场可编程逻辑门阵列)。本具体实施方式中所述第一处理器102和所述第二处理器112均包括型号为stm32f407zgt6的芯片。

36.可选的,所述上位机单元10还包括与所述第一处理器102电连接的第一外围电路106,所述第一外围电路106包括:第一晶振电路、第一复位电路和第一烧写电路,所述第一晶振电路用于产生所述第一处理器102的工作频率;所述第一复位电路用于对所述第一处理器102进行硬件复位;所述第一烧写电路用于对所述第一处理器102进行程序烧录;

37.所述移动单元11还包括与所述第二处理器112电连接的第二外围电路116,所述第二外围电路116包括:第二晶振电路、第二复位电路和第二烧写电路,所述第二晶振电路用于产生所述第二处理器112的工作频率;所述第二复位电路用于对所述第二处理器112进行硬件复位;所述第二烧写电路用于对所述第二处理器112进行程序烧录。

38.具体来说,所述第一晶振电路和所述第二晶振电路可以均为32mhz晶振电路,所述第一复位电路和所述第二复位电路均为按键复位电路,所述第一烧写电路和所述第二烧写电路均包括型号为ch340g的芯片。

39.所述第一处理器102还包括第一存储电路和第一串口控制电路,所述第一存储电路用于在所述第一处理器102在对所述第一光信号l1进行调制或者对所述第二光信号l2进行解调时载波信号的存储,所述第一串口控制电路用于控制所述第一处理器102的串口通信。所述第二处理器112还包括第二存储电路和第二串口控制电路,所述第二存储电路用于

在所述第二处理器112在对所述第二光信号l2进行调制或者对所述第一光信号l1进行解调时载波信号的存储,所述第二串口控制电路用于控制所述第二处理器112的串口通信。在一示例中,所述第一存储电路和所述第二存储电路均包括型号为w25q16的芯片。

40.可选的,所述移动单元11还包括:

41.电源结构117,包括第二usb接口,用于与外界移动电源连接,用于向所述存储器111、所述第二处理器112、所述第二模式选择电路115、所述第二控制电路113、以及所述第二量子阱二极管芯片114供电。

42.举例来说,所述电源结构通过所述第二usb(universal serial bus,通用串行总线)结构电连接来自于外界的所述移动电源,以向所述移动单元11中的各电子元器件(例如所述存储器111、所述第二处理器112、所述第二模式选择电路115、所述第二控制电路113、以及所述第二量子阱二极管芯片114)进行5v供电。其中,所述移动电源可以是但不限于移动充电宝、电池等。

43.可选的,所述移动单元10还包括:

44.输入结构,用于接收来自外部的触发信号,以触发所述存储器111向所述上位机单元10发送所述第二光信号l2。

45.可选的,所述输入结构为物理按键、设置于所述移动单元11中的显示屏上的虚拟按键、或者传感器。具体来说,触发所述存储器111向所述上位机单元10发送所述第二光信号l2的触发方式可以是物理按键触发、软件定义触发或者传感器触发。

46.可选的,所述第一驱动电路包括第一发送信号放大电路、以及与所述第一发送信号放大电路电连接的第一偏置电路,所述第一接收电路包括第一跨阻放大电路、与所述第一跨阻放大电路电连接的第一接收信号放大电路、以及与所述第一接收信号放大电路电连接的第一比较器电路;

47.所述第二驱动电路包括第二发送信号放大电路、以及与所述第二发送信号放大电路电连接的第二偏置电路,所述第二接收电路包括第二跨阻放大电路、与所述第二跨阻放大电路电连接的第二接收信号放大电路、以及与所述第二接收信号放大电路电连接的第二比较器电路。

48.所述第一发送信号放大电路包括第一功率放大器,所述第一功率放大器的作用在于提升所述第一处理器产生的信号功率,以便其具有足够的驱动能力,从而可以加载至第一量子阱二极管芯片上进行发送。所述第一偏置电路可以包括直流偏置电路或者是mos管,所述第一偏置电路的作用是给所述第一量子阱二极管提供恒定的使其处于开启状态的电压,让信号的变化在其开启阶段。所述第二发送信号放大电路的结构可以与所述第一发送信号放大电路的结构相同。所述第二偏置电路的结构可以与所述第一偏置电路的结构相同。

49.在一示例中,所述第一发送信号放大电路、所述第一接收信号放大电路、所述第二发送信号放大电路和所述第二接收信号放大电路均包括型号为ad8015的芯片。所述第一偏置电路和所述第二偏置电路均包括bias-t器件。所述第一跨阻放大电路和所述第二跨阻放大电路均包括型号为opa2677的芯片。所述第一比较器电路和所述第二比较器电路均包括型号为max9016的芯片。

50.可选的,所述第一接收电路包括第一跨阻放大器、与所述第一跨阻放大器电连接

的第一电压放大器和与所述第一电压放大器电连接的第一电压比较器;

51.所述第二接收电路包括第二跨阻放大器、与所述第二跨阻放大器电连接的第二电压放大器和与所述第二电压放大器电连接的第二电压比较器。

52.具体来说,所述第一量子阱二极管芯片中的所述第一量子阱二极管将接收到的所述第二光信号l2转换为第二光电流信号,所述第一跨阻放大器用于将所述第二光电流信号转换为第二光电压信号。所述第一电压放大器用于将微弱所述第二光电压信号放大至0v~5v范围,以便于所述第一电压比较器进行比较。所述第一电压比较器用于将放大后的所述第二光电压信号由模拟信号转换为数字信号,以便于后续所述第一处理器102进行处理。所述第二量子阱二极管芯片中的所述第二量子阱二极管将接收到的所述第一光信号转换为第一光电流信号,所述第二跨阻放大器用于将所述第一光电流信号转为第一光电压信号。所述第二电压放大器用于将微弱的所述第一光电压信号放大至0v~5v范围,以便于所述第二电压比较器进行比较。所述第二电压比较器用于将放大后的所述第一光电压信号由模拟信号转换为数字信号,以便于后续所述第二处理器112进行处理。

53.为了提升接收信号的信噪比,可选的,所述第一接收电路还包括位于所述第一跨阻放大器和所述第一电压放大器之间的第一带通滤波器;

54.所述第二接收电路还包括位于所述第二跨阻放大器和所述第二电压放大器之间的第二带通滤波器。

55.举例来说,当所述上位机单元10处于发送模式时,所述第一模式选择电路105的控制端为低电平,选通发送通路(即选通所述第一驱动电路),所述第一控制电路103的输入信号为经过ook调制之后的数字信号,低电平为0v,高电平为3.3v,所述第一控制电路103的输出信号为经过信号处理后,具有2.5v偏置电压、峰值为1v的数字信号,以适配所述第一量子阱二极管芯片104的开启电压;当所述上位机单元10处于接收模式时,所述第一模式选择电路105的控制端为高电平,选通接收通路(即选通所述第一接收电路),所述第一量子阱二极管芯片104接收到外部的光学信号(即所述第二光信号l2)后,产生约为100na的光电流,经过跨阻放大、一级放大后,其低电平电压范围为0~0.3v,高电平电压范围为2.5v~4.5v,因此经过所述第一比较器电路之后,可以转换为0v低电平,5v高电平的数字信号,送入所述第一处理器102中进行解调处理。

56.当所述移动单元11处于发送模式时,所述第二模式选择电路115的控制端为低电平,选通发送通路(即选通所述第二驱动电路),所述第二控制电路113的输入信号为经过ook调制之后的数字信号,低电平为0v,高电平为3.3v,所述第二控制电路113的输出信号为经过信号处理后,具有2.5v偏置电压、峰值为1v的数字信号,以适配所述第二量子阱二极管芯片114的开启电压;当所述移动单元11处于接收模式时,所述第二模式选择电路115的控制端为高电平,选通接收通路(即选通所述第二接收电路),所述第二量子阱二极管芯片114接收到外部的光学信号(即所述第一光信号l1)后,产生约为100na的光电流,经过跨阻放大、一级放大后,其低电平电压范围为0~0.3v,高电平电压范围为2.5v~4.5v,因此经过所述第二比较器电路之后,可以转换为0v低电平,5v高电平的数字信号,送入所述第二处理器112中进行解调处理。

57.可选的,所述第一驱动电路的结构与所述第二驱动电路的结构相同,所述第一接收电路的结构与所述第二接收电路的结构相同,所述第一模式选择电路105的结构与所述

第二模式选择电路115的结构相同。

58.可选的,所述第一模式选择电路包括第一模拟开关,所述第一模拟开关包括第一正电压输入端、第一接地端、第一控制端、第一共同输出端、第一上位机输入端和第二上位机输入端,所述第一上位机输入端电连接所述第一驱动电路,所述第二上位机输入端电连接所述第一接收电路;

59.所述第二模式选择电路包括第二模拟开关,所述第二模拟开关包括第二正电压输入端、第二接地端、第二控制端、第二共同输出端、第一移动单元输入端和第二移动单元输入端,所述第一移动单元输入端电连接所述第二驱动电路,所述第二移动单元输入端电连接所述第二接收电路。

60.可选的,所述第一模拟开关和所述第二模拟开关均为型号为ts5a23157的模拟开关。

61.具体来说,所述第一模拟开关中的所述第一正电压输入端被提供5v电压,所述第一接地端被提供0v的电压,以使所述第一模拟开关正常工作;同时所述第一共同输出端com用来连接所述第一量子阱二极管芯片的信号所述第一上位机输入端电连接所述第一驱动电路,所述第二上位机输入端电连接所述第一接收电路,根据所述第一控制端上的电平不同,选择不同的通路(即选择所述第一驱动电路导通或者所述第一接收电路导通)。本领域技术人员也可以根据实际需要选择其他型号的多路复用器来构成所述第一模式选择电路和所述第二模式选择电路。

62.所述第一量子阱二极管芯片104中的所述第一量子阱二极管和所述第二量子阱二极管芯片114中的所述第二量子阱二极管均为gan基量子阱二极管信号,且gan基量子阱二极管信号的发射光谱与探测光谱存在重叠区域,因而使得所述第一量子阱二极管和所述第二量子阱二极管均具有发光和探测共存的物理现象,可以在照明的同时对外部光信号进行探测,即所述第一量子阱二极管芯片104和所述第二量子二极管芯片114均可以作为光发射器件和光接收器件。为了进一步简化所述基于量子阱二极管的闪存装置的制造工艺,可选的,所述第一量子阱二极管芯片104的结构和所述第二量子阱二极管芯片114的结构相同;

63.所述第一量子阱二极管芯片104为发射波长为470nm的蓝光芯片;或者,所述第一量子阱二极管芯片104为发射波长为520nm的绿光芯片,从而使得所述第一量子阱二极管芯片104的发射光谱与接收光谱之间的重叠区较宽,例如所述第一量子阱二极管芯片104为发射波长为520nm的绿光芯片时,发射光谱与接收光谱的重叠区宽度为40nm。

64.可选的,所述第一量子阱二极管芯片包括第一衬底、位于所述第一衬底上的第一量子阱阵列、以及位于所述第一衬底与所述第一量子阱阵列之间的反射镜,所述第一量子阱阵列包括呈阵列排布的多个所述第一量子阱二极管;

65.所述第一量子阱二极管芯片包括第二衬底、以及位于所述第二衬底上的第二量子阱阵列,所述第二量子阱阵列包括呈阵列排布的多个所述第二量子阱二极管,所述第二量子阱二极管为反向偏压二极管。

66.在一示例中,所述反射镜可以为dbr(distributed bragg reflection,分布式布拉格反射镜),以提升其出光性能,提高光聚合程度。多个所述第一量子阱二极管排布形成所述第一量子阱阵列,可以提高所述第一量子阱二极管芯片的出光性能以及光聚合程度。同样的,多个所述第二量子阱二极管也排布成第二量子阱阵列,以加大所述第二量子阱二

极管芯片的发射功率,以提高其通信的距离和范围。所述第二量子阱二极管为反向偏压二极管,可以提高所述第二量子阱二极管的接收灵敏度。

67.可选的,所述第一信息和所述第二信息均为图片信息、音频信息、或者视频信息。

68.本具体实施方式提供的基于量子阱二极管的闪存装置进行数据存储的工作流程如下:当从所述主机101向所述移动单元111进行数据存储时,所述主机101通过所述第一usb接口发送所述第一信息的数据流到所述第一处理器102中,所述第一处理器102对所述第一信息进行ook调制,转化为第一发送电学信号,并通知所述第一模式选择电路105,开启发送模式(即选通所述第一驱动电路),所述第一控制电路103接收到所述第一发送电学信号后,进行放大、加偏置等处理,转化为第二发送电学信号,该信号与所述第一量子阱二极管芯片104匹配,并经过所述第一量子阱二极管芯片104转化为所述第一光信号l1进行发送。当不考虑时间差时,所述第一光信号l1被所述第二量子阱二极管芯片114进行接收,产生第三接收电学信号,送入所述第二控制电路113,在所述第二控制电路113中经过跨阻放大、二级放大、第二比较器处理之后,产生第四接收电学信号,即为在所述第二处理器112的端口处产生的ook调制信号,所述第二处理器112对信号进行ook解调,通过串口送入所述存储器111中进行存储。

69.本具体实施方式提供的基于量子阱二极管的闪存装置进行数据读取的工作流程如下:当需要从所述移动单元中读取数据时,外界通过按键/软件控制等方式,控制所述存储器111向所述第二处理器112发送所述第二信息,所述第二处理器112对所述第二信息进行ook调制后,产生第三发送电学信号,送入所述第二控制电路113进行放大,加偏置等处理后,转化为第四发送电学信号,所述第四发送电学信号与所述第二量子阱二极管芯片114匹配,并经过所述第二量子阱二极管芯片114转化为所述第二光信号进行发送。不考虑时间差时,所述第二光信号被所述第一量子阱二极管芯片104接收,产生第一接收电学信号,送入所述第一控制电路103,在其中经过跨阻放大、二级放大、第一比较器处理后,产生第二接收电学信号,即为在所述第一处理器102的端口处产生的ook调制信号,所述第一处理器对所述第二接收电学信号进行ook解调,通过串口送入所述主机101中进行显示。

70.本具体实施方式提供的基于量子阱二极管的闪存装置,通过设置上位机单元和移动单元,且所述上位机单元能够向所述移动单元发射第一光信号以及接收来自所述移动单元的第二光信号,所述移动单元能够向所述上位机单元发送所述第二光信号、并接收来自于所述上位机单元的所述第一光信号,使得所述基于量子阱二极管的闪存装置实现了光存储功能、光探测功能、光发射功能的融合集成,从而极大的扩展了所述基于量子阱二极管的闪存装置的功能,扩大了所述基于量子阱二极管的闪存装置的应用领域。同时,可见光通信的方式传输稳定、受外界干扰小、传输速率快等优点,使得所述基于量子阱二极管的闪存装置的性能得到了改善。而且,本具体实施方式提供的基于量子阱二极管的闪存装置其核心芯片成本低廉、集成度高、设备体积小,作为一种新型技术路线,进一步扩展了移动存储技术的选择方案,极大提高了u盘类等闪存装置的经济性和科技感。

71.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1