存储器芯片测试方法及相关设备与流程

1.本公开涉及集成电路测试技术领域,具体而言,涉及一种存储器芯片的测试方法、装置、测试设备、电子设备及可读存储介质。

背景技术:

2.相关技术中,通过自动化测试设备(automatic test equipment,ate)对存储器芯片进行测试的测试覆盖范围全面、但时间较长,如此,测试成本较高。同时,由于通过ate对存储芯片测试时的测试频率较低,很难对存储芯片进行全速(at-speed)测试。

3.而由于存储器内建自测试(memory build-in-self test,mbist)电路集成在存储芯片内部,比较容易实现at-speed测试,但通过mbist电路对存储芯片进行测试的测试覆盖范围有限,因此,提供一种既可以进行at speed测试,同时测试覆盖范围全面、测试成本较低的测试方法是亟待解决的技术问题。

技术实现要素:

4.本公开的目的在于提供一种存储器芯片的测试方法、装置、测试设备、计算机设备及可读存储介质,能够减少测试产生的面积开销,减少测试设备的使用时间,从而减少测试成本。

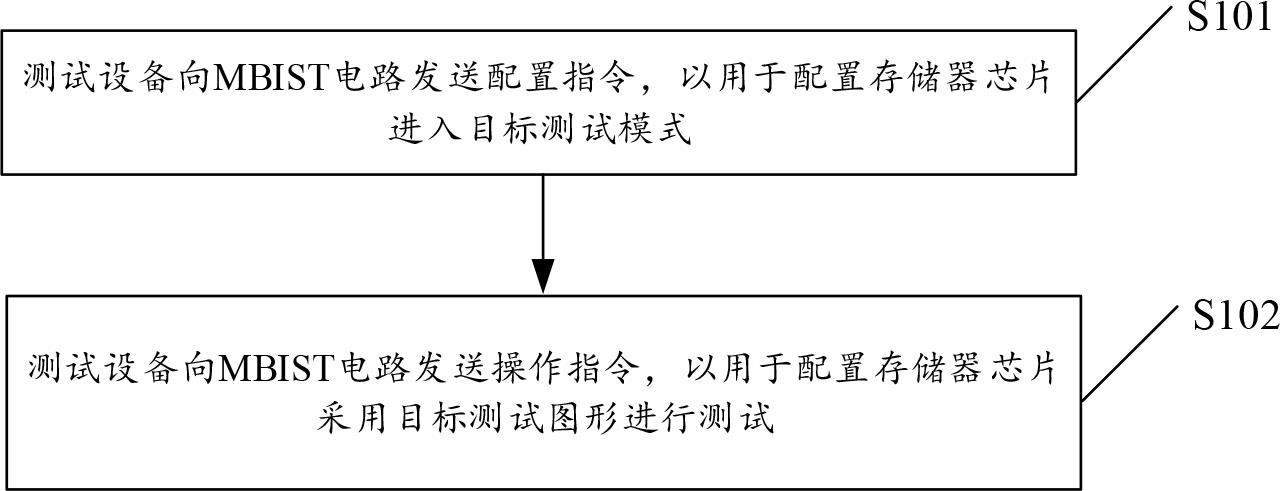

5.本公开实施例提供了一种存储器芯片测试方法,所述存储器芯片中包括mbist电路,所述方法包括:测试设备向所述mbist电路发送配置指令,以用于配置所述存储器芯片进入目标测试模式;所述测试设备向所述mbist电路发送操作指令,以用于配置所述存储器芯片采用目标测试图形进行测试。

6.本公开实施例还提供了一种内建自测试电路,包括:控制电路,用于接收并解析测试设备发送的配置指令和操作指令,根据解析结果生成控制信号;信号生成电路,用于接收并根据所述控制信号生成对存储器芯片进行测试时的测试图形信号、测试指令信号、测试地址信号和测试时钟频率信号,以对存储器芯片进行测试。

7.本公开实施例另提供了一种测试设备,包括:发送单元,用于向mbist电路发送配置指令,以配置存储器芯片进入目标测试模式,所述存储器芯片中包括所述mbist电路;所述发送单元,还用于向所述mbist电路发送操作指令,以配置所述存储器芯片采用目标测试图形,进行测试。

8.本公开实施例再提供了一种电子设备,包括:一个或多个处理器;存储器,配置为存储一个或多个程序,当所述一个或多个程序被所述一个或多个处理器执行时,使得所述电子设备实现上述公开实施例所述的方法。

9.本公开实施例另外提供了一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,当所述计算机程序在计算机上运行时,使得所述计算机执行上述公开实施例所述的方法。

附图说明

10.图1是本公开一示例性实施例提供的一种存储器芯片测试方法的实现流程示意图。

11.图2是本公开另一示例性实施例提供的一种存储器芯片测试方法的实现流程示意图。

12.图3是本公开一示例性实施例中单个bank(存储体)中地址寻址顺序的示意图。

13.图4是本公开一示例性实施例中的配置指令的组成示意图。

14.图5是本公开本公开一示例性实施例中的配置指令中的第2位至第9位的组成示意图。

15.图6是本公开本公开一示例性实施例中的操作指令中的第1位至第5位的组成示意图。

16.图7是本公开一示例性实施例中的mbist电路的组成结构示意图。

17.图8是本公开一示例性实施例中的mbist控制电路的示意图。

18.图9是本公开一示例性实施例的时钟生成电路的示意图。

19.图10是本公开一示例性实施例的指令生成电路的示意图。

20.图11是本公开一示例性实施例的地址生成电路的示意图。

21.图12是本公开一示例性实施例中的数据生成电路的示意图。

22.图13是本公开一示例性实施例中的ate控制存储器芯片中mbsit电路进行测试的总体框图。

23.图14是本公开一示例性实施例的ate与mbist交互的具体电路图。

24.图15是本公开一示例性实施例的一种测试设备的组成结构示意图。

具体实施方式

25.附图仅为本公开的示意性图解,图中相同的附图标记表示相同或类似的部分,因而将省略对它们的重复描述。附图中所示的一些方框图是功能实体,不一定必须与物理或逻辑上独立的实体相对应。可以采用软件形式来实现这些功能实体,或在一个或多个硬件模块或集成电路中实现这些功能实体,或在不同网络和/或处理器装置和/或微控制器装置中实现这些功能实体。下面结合附图对本公开实施方式提供的存储器进行详细说明。

26.相关技术中,mbist电路是建立在存储器芯片内部的测试电路,mbist电路被激活后可以自己控制测试电路的运行,实现对存储器芯片的测试。mbist电路一般面积很小(主要和实现测试算法的复杂度以及实现方式有关),测试故障覆盖范围有限。ate对存储器芯片进行测试时,由于测试频率较低,很难进行at-speed测试,由于测试时间较长且ate价格昂贵,因此,测试时间越长意味着成本越高。基于上述技术问题,本公开实施例提供了一种将mbist电路和ate相结合的存储器芯片测试方法。

27.图1是本公开一示例性实施例提供的一种存储器芯片测试方法的实现流程示意图。图1的存储器芯片中可以包括mbist电路。如图1所示,该存储器芯片测试方法可以包括以下步骤:步骤s101:测试设备向mbist电路发送配置指令,以用于配置存储器芯片进入目标测试模式。

28.这里,存储器芯片可以是包括mbist电路的动态随机存取存储器(dynamic random access memory,dram)或同步动态随机存取存储器(synchronous dynamic random access memory,sdram),例如,存储芯片可以是双倍速率同步动态随机存储器(dual data rate sdram,ddr sdram)或低功耗双倍速率同步动态随机存储器(low power dual data rate sdram,lpddr sdram)。当然也可以是需要进行测试的其它存储器芯片,这里不进行具体限定。例如,存储器芯片可以是ddr5 sdram。测试设备可以是ate,或其它能够对存储器芯片进行测试的设备。

29.可以理解的是,目标测试模式可以反映对存储器芯片进行测试时的环境信息,这里的环境信息可以至少包括时钟频率、操作时序、写入数据、压缩模式等中的至少一种或者多种。

30.目标测试模式可以根据对存储器芯片进行测试时对存储器芯片设置的时钟频率和设置的压缩模式(选择并行模式),确定对应的测试模式为目标测试模式。

31.在本公开的一些实施方式中,配置指令可以是包括第一预设位数的指令,例如,第一预设位数可以是13位。其中,13位配置指令中的每一位可以预先设置用于配置对存储器芯片进行测试时的不同环境信息。

32.步骤s102:测试设备向mbist电路发送操作指令,以用于配置存储器芯片采用目标测试图形进行测试。

33.在一些可能的实施方式中,目标测试图形可以是表示向mbist电路发送的测试数据。

34.可以理解的是,操作指令可以反映进行测试时的读写的方式、读写操作和地址寻址的寻址顺序。

35.在本公开一种可能的实施方式中,操作指令可以是包括第二预设位数的指令,例如,第二预设位数可以是5位。其中,5位操作指令中的每一位可以预先设置用于配置对存储器信息进行测试时的具体测试方式。

36.本公开实施例中,通过测试设备向存储器芯片包括的mbist电路发送配置指令和操作指令,以确定mbist电路对存储器芯片进行测试时的目标测试模式和目标测试图形,实现不同测试模式和不同目标测试图形下对存储器芯片的测试,测试覆盖范围全面,且在不同测试模式包括at speed模式时,可以进行at speed测试,同时通过复用mbist电路的方式,可以最大程度减少测试产生的面积开销,同时减少测试设备的使用时间,减少测试成本。

37.图2是本公开另一示例性实施例提供的一种存储器芯片测试方法的实现流程示意图。如图2所示,该存储器芯片测试方法可以包括以下步骤:步骤s201:测试设备向mbist电路发送内建自测试使能信号,以用于触发开启mbist电路针对存储器芯片的测试。

38.在本公开一些可能的实施方式中,内建自测试使能信号可以是第一电平的信号或第二电平的信号,需要根据mbist电路确定。第一电平可以是逻辑“0”,第二电平可以是逻辑“1”,但本公开并不限定于此。

39.在一些可能的实施方式中,触发开启mbist电路针对所述存储器芯片的测试的实现方式,可以是触发mbist电路中的bist控制电路开始工作,以通过bist控制电路对测试设

备发送的配置指令和操作指令进行解析,根据解析出的配置信号和操作信号对存储器芯片进行对应的测试。

40.步骤s202:测试设备向mbist电路发送配置指令,以用于配置存储器芯片进入目标测试模式。

41.步骤s203:测试设备向mbist电路发送操作指令,以用于配置存储器芯片采用目标测试图形进行测试。

42.本公开实施例中,通过测试设备向mbist电路发送内建自测试使能信号,可以触发开启mbist电路针对存储器芯片的测试,有利于mbist电路根据接收的配置指令和操作指令对存储器芯片在目标测试模式和目标测试图形的配置下进行对应的测试。

43.在本公开的实施例中,配置指令中可以包括压缩模式配置位,压缩模式配置位可以用于设置对存储器芯片进行测试时采用的目标压缩模式,目标压缩模式可以用于确定目标测试模式。

44.在一种可能的实施方式中,配置指令中还可以包括时钟频率配置位,时钟频率配置位可以用于设置对存储器芯片进行测试时的目标时钟频率;目标压缩模式可以和目标时钟频率一起确定目标测试模式。

45.可以理解的是,时钟频率配置位的不同值对应不同的目标时钟频率。压缩模式配置位的不同值对应不同的目标压缩模式,时钟频率和压缩模式的不同组合可以确定多个测试模式,如下表1所示。

46.表1

47.如表1所示,在时钟频率包括时钟频率1和时钟频率2(2个不同时钟频率),压缩模式包括压缩模式1、压缩模式2和压缩模式3类(3个不同压缩模式)的情况下,可以确定6个测试模式。但实际上在对存储器芯片的测试中,不存在6个测试模式的,可能只存在3个。可以看出,对于目标时钟频率和目标压缩模式对应的目标测试模式可以通过上表1进行查询。

48.本公开实施例中,通过配置指令中的压缩模式配置位可以确定对存储器芯片进行测试时的目标压缩模式,从而可以根据目标压缩模式确定对存储器芯片进行测试的目标测试模式,以便于mbist电路针对存储器芯片在目标测试模式下进行测试。

49.在本公开的一些实施例中,目标压缩模式可以为压缩模式、无压缩模式中的一种。其中:当目标压缩模式为压缩模式时,目标时钟频率可以配置为第一时钟频率值;当目标压缩模式为无压缩模式时,目标时钟频率可以配置为第二时钟频率值。

50.在本公开的一些实施方式中,第一时钟频率值可以不是(小于)美国半导体标准行业协会(joint electron device engineering council,jedec)要求的频率值,例如,第一时钟频率值可以是5ns(纳秒);第二时钟频率值可以是满足jedec要求的频率值,例如,第二频率值可以是2.5ns。

51.在一些可能的实施方式中,在存储器芯片包括8个存储体组(bank group,bg),每个bg包括4个逻辑存储体(bank),总共包括32个逻辑存储体时,压缩模式可以至少包括存储体组压缩模式和存储体压缩模式,其中,存储体组压缩模式可以是8bg的压缩模式,这里,

8bg的压缩模式可以用于常规模式,存储体压缩模式可以是32banks的压缩模式, 32banks压缩模式可以用于老化模式。

52.这里,8bg的压缩模式的压缩模式可以是对8个bg中的每一bg中的一bank同时压缩,例如,bg1、bg2、bg3、bg4、bg5、bg6、bg7和bg8中每个bg中的bank0均同时压缩,这里,也可以是对bg1、bg2、bg3、bg4、bg5、bg6、bg7和bg8中每个bg中的bank0均同时进行测试。

53.在本公开的一些实施方式中,常规模式可以是指电压、温度等测试环境与host端一致的测试模式,这里host端可以为用户端,可以指存储器芯片与中央处理器(central processing unit,cpu)封装在一起成为成品后提供给到用户使用时的情况。考虑到存储器芯片中的电压源分布情况与负载等实际问题,在存储芯片为ddr5时可以采用8bank的压缩模式来减少测试时间,相应的时序上将无法满足全速测试。

54.在本公开的一些实施方式中,无压缩模式可以用于全速(at speed)模式,全速模式可以是不存在多个bank同时压缩的情况,例如,在包括8个bg,每个bg包括4个bank,总共包括32个bank时,无压缩模式可以是指一个bank测试完再进入下一个bank测试,依次测试完成32个bank,不存在多个bank同时测试的情况。

55.在本公开的一些实施方式中,全速模式可以是指测试频率达到jedec要求的频率的测试模式。例如,在测试存储器芯片的a信号时,a信号需要满足的时序为10ns,那么只要能让a信号持续10ns,对于a信号的测试来说就是at_speed测试模式。

56.可以理解的是,常规模式和at_speed测试模式的区别在于测试频率不同,压缩模式不同,常规测试的测试频率不满足jedec要求的时序,at_speed测试的测试频率满足jedec要求的时序,常规测试的压缩模式为存储体压缩模式,at speed测试的压缩模式为无压缩模式;而老化测试的测试频率可以是常规测试相同,均不满足jedec要求的时序,但老化测试的压缩模式可以是存储体压缩模式,参见与表1对应的下表2。

57.表2

58.在本公开的一些实施例中,存储体压缩模式可以是存储器芯片中的每一bank同时压缩的情况,例如,在包括8个bg,每个bg包括4个bank,总共包括32个bank时,存储体压缩模式可以是指32个bank同时进行测试的情况。

59.本公开实施例中,通过当目标测试模式为压缩模式时,将目标时钟频率配置为第一时钟频率值,当目标测试模式为无压缩模式时,将目标时钟频率配置为第二时钟频率值,如此,可以通过配置对存储器芯片测试的时钟频率值,通过mbist电路可以实现存储器芯片的压缩模式和全速模式下的测试。

60.在本公开的一些实施例中,配置指令中还可以包括操作时序配置位,操作时序配置位可以用于设置对存储器芯片进行测试时的目标操作时序。

61.本公开实施例中,通过将包括操作时序配置位的配置指令发送给mbist电路,使得mbist电路可以对时序配置位进行解析从而确定出对存储器芯片进行测试时的时序配置位的配置对应的操作时序,从而对存储器芯片按照操作时序进行测试。

62.在本公开的一些实施例中,配置指令中还可以包括写入数据配置位,写入数据配置位可以用于设置对所述存储器芯片进行测试时的目标写入数据。

63.这里,可以预先建立数据写入配置位上的值与写入数据之间的对应关系,数据写入配置位上值与写入数据之间的对应关系可以参考表3。

64.表3

65.可以理解的是,写入数据配置位上的不同值对应不同的写入数据,写入数据配置位上的值与写入数据之间存在一一对应关系。

66.本公开实施例中,通过将包括写入数据配置位的配置指令发送给mbist电路,使得mbist电路可以对写入数据配置位的值进行解析从而确定出对存储器芯片进行测试时的写入数据配置位的值对应的写入数据,从而对存储器芯片写入对应的写入数据进行测试。

67.在本公开的一些实施方式中,操作指令中可以包括读写方式配置位、地址寻址顺序配置位和读写操作配置位。其中:读写方式配置位可以用于设置对存储器芯片进行测试时所采用的目标读写方式;地址寻址顺序配置位可以用于设置对存储器芯片进行测试时所采用的目标地址寻址顺序;读写操作配置位可以用于设置对存储器芯片进行测试时所采用的目标读写操作;目标写入数据、目标读写方式、目标地址寻址顺序和目标读写操作可以用于确定目标测试图形。

68.本公开实施例中,通过操作指令中的读写方式配置位可以确定对存储器芯片进行测试时的读写方式,通过操作指令中的地址寻址顺序配置位可以确定对存储器芯片进行测试时的地址寻址顺序,通过操作指令中的读写操作配置位可以确定对存储器芯片进行测试时进行读操作还是写操作,从而可以根据目标读写方式、目标读写顺序和目标读写操作确定对存储器芯片进行测试的目标测试图形,以便于mbist电路针对存储器芯片在目标测试图形下进行测试。

69.本公开的一些实施方式中,目标读写方式可以是列优先读写方式(y fast)、列页优先读写方式(y page fast)和行优先读写方式(x fast)中的一种,需要根据读写方式配置位上的值来确定,可以定义读写方式配置位上不同的值可以对应不同的读写方式。

70.在一些可能的实施方式中,x fast可以是指按照x方向优先寻址,即row行优先寻址,针对每一bank的同一列的每一行中的存储单元顺序执行激活(act)-写或读(wr/rd)-预充电(pre);y fast可以是指按照y方向优先寻址,即列优先寻址,针对每一bank的同一行的每一列中的存储单元顺序执行激活(act)-写或读(wr/rd)-预充电(pre);y page fast可以同样是指按照y方向优先寻址,即列优先寻址,不过其会在列遍历完bank的每一行的全部列后才执行预充电(pre),即激活(act)-写或读(wr/rd)-(wr/rd)...-预充电(pre)。

71.图3是本公开一示例性实施例中单个bank中地址寻址顺序的示意图。如图3所示,其中,3a可以是一示例性实施例中单个bank中x fast地址寻址顺序的示意图;图3中的3b可以是一示例性实施例中单个bank中y fast地址寻址顺序的示意图;图3中的3c可以是一示例性实施例中单个bank中y pagefast地址寻址顺序的示意图。

72.3a中x方向表示bank的存储阵列的行,y方向表示bank的存储阵列的列,折线301可

以是z字形,表示寻址顺序是从bank的第一行第一一列的第一个存储单元开始寻址直至寻址完第一列的每一行的全部存储单元,然后进入bank的第二列开始寻址

……

如此,依次寻址完整个bank。

73.3b中x方向表示bank的存储阵列的行,y方向表示bank的存储阵列的列,折线302可以是将折线301旋转90

°

后再进行镜像得到的折线,表示寻址顺序是从bank的第一行第一列的第一个存储单元开始寻址直至寻址完第一行的每一列的全部存储单元,然后进入bank的第二行开始寻址

……

如此,依次寻址完整个bank。

74.3c中x方向表示bank的存储阵列的行,y方向表示bank的存储阵列的列,折线303可以与折线302完全相同表示的寻址顺序也完全相同。

75.可以理解的是,与y方向平行的一条线上的所有存储单元表示同一行(行地址相同),与x方向平行的一条线上的所有存储单元表示同一列(表示列地址相同)。

76.本公开的一些实施方式中,目标地址寻址顺序可以包括地址递增寻址顺序、地址递减寻址顺序、缺省寻址和跳跃寻址中的一种,需要根据地址寻址顺序配置位上的值来确定,可以定义地址寻址顺序配置位上不同的值可以对应不同的目标地址寻址顺序。

77.在本公开的一些实施例中,目标读写操作可以为读操作和写操作中的一种,需要根据读写操作配置位上的值来确定,可以定义读写操作配置位上不同的值对应不同的操作。

78.本公开实施例中,由于目标读写方式包括列优先读写方式、列页优先读写方式和行优先读写方式中的一种,目标地址寻址顺序包括地址递增寻址顺序、地址递减寻址顺序、缺省寻址和跳跃寻址中的一种,目标读写操作为读操作和写操作中的一种,如此,可以针对不同的目标读写方式、不同的目标寻址方式和不同的目标读写操作形成多种不同的读写操作,以便于再配合读写数据以及测试环境的变化满足存储器芯片测试的大多数测试需求。

79.在本公开的一些可能的实施例中,在存储器芯片为16gb的ddr5的情况下,配置指令可以包括13位。其中:配置指令中的第1位可以用于配置对存储器芯片进行测试时的目标时钟频率,当配置指令中的第1位取值为第一值时,目标时钟频率可以配置为第一时钟频率值,配置指令中的第1位取值为第二值时,时钟频率配置可以为第二时钟频率值;配置指令中的第2位至第9位可以用于配置对存储器芯片进行测试时的目标操作时序;配置指令中的第10位至第11位可以用于配置对存储器芯片进行测试时的目标写入数据,当配置指令中的第10位至第11位取值为第三值时,配置的目标写入数据可以为全0;当配置指令中的第10位至第11位取值为第四值时,配置的目标写入数据可以为01交替;当配置指令中的第10位至第11位取值为第五值时,配置的目标写入数据可以为10交替;当取值为第六值时,配置的目标写入数据可以为全1;配置指令中的第12位至第13位可以用于配置对存储器芯片进行测试时采用的目标压缩模式,当配置指令中的第12位至第13位取值为第三值时,配置的目标压缩模式可以为无压缩模式;当配置指令中的第12位至第13位取值为第四值时,配置的目标压缩模式可以为存储体组压缩模式;当所述配置指令中的第12位至第13位取值为第五值时,配置的目标压缩模式可以为存储体压缩模式;目标时钟频率和目标压缩模式用于确定目标测试模式。

80.图4是本公开一示例性实施例中的配置指令的组成示意图。

81.如图4所示,配置指令包括13位[0:12],其中,第一位[0]可以是时钟频率tck,对应

时钟频率配置位;第2位至第9位[1:8]可以是时序timing,对应操作时序配置位;第10位和第11位[9:10]可以是测试数据data,对应写入数据配置位,第12位和第13位[11:12]可以是压缩compress对应压缩模式配置位。

[0082]

在本公开实施例中,第一值可以是二进制的0,第二值可以是二进制的1。第一时钟频率值可以是5ns,第二时钟频率值可以是2.5ns,即,当tck=0时的目标时钟频率可以为5ns,tck=1时的目标时钟频率可以为2.5ns,参见表4。

[0083]

表4

[0084]

在本公开的一些实施方式中,第三值可以是00,第四值可以是01,第五值可以是10,第六值可以是11,对应的目标写入数据可以参见下表5,对应的目标压缩模式可以参见下表6。

[0085]

表5

[0086]

表6

[0087]

其中,1bank可以表示一个bank一个bank测试的无压缩模式;8bg可以表示8个bank group中的每个bank group中的bank0或bank1同时测试的存储体压缩模式;32banks可以表示存储器芯片中的32个bank同时测试的存储体压缩模式。

[0088]

本公开实施例中,通过对13位配置指令中的对应配置位配置不同的值,可以设置不同的目标时钟频率、不同的目标操作时序、不同的目标写入时序和不同的目标压缩模式,从而可以实现对不同测试环境和测试模式的配置,有利于mbist电路通过配置指令对存储器芯片进行不同测试环境和测试模式的测试。

[0089]

在本公开的一些实施方式中,配置指令中的第2位至第3位可以用于配置第一时延,第4位至第5位可以用于配置第二时延,第6位至第7位可以用于配置第三时延,第8位至第9位可以用于配置第四时延,第一时延、第二时延、第三时延和第四时延可以用于确定目标操作时序。其中:当配置指令中的第2位至第3位取值为第三值时,第一时延可以配置为第一时延值;当配置指令中的第2位至第3位取值为第四值时,第一时延可以配置为第二时延值;当配置指令中的第2位至第3位取值为第五值时,第一时延可以配置为第三时延值;当配置指令中的第2位至第3位取值为第六值时,第一时延配置可以为第四时延值;当配置指令中的第4位至第5位取值为第三值时,第二时延可以配置为第一时延值;当配置指令中的第4位至第5位取值为第四值时,第二时延配置可以为第二时延值;当配置指令中的第4位至第5位取值为第五值时,第二时延可以配置为第三时延值;当配置指令中的第4位至第5位取值为第六值时,第二时延配置可以为第四时延值;当配置指令中的第6位至第7位取值为第三值时,第三时延可以配置为第三时延值;当配置指令中的第6位至第7位取值为第四值时,第三时延可以配置为第四时延值;当配置指令中的第6位至第7位取值为第五值时,第三时延可以配置为第五时延值;当配置指令中的第6位至第7位取值为第四值时,第三时延可以配

置为第六时延值;当配置指令中的第8位至第9位取值为第三值时,第四时延配置可以为第一时延值;当配置指令中的第8位至第9位取值为第四值时,第四时延可以配置为第二时延值;当配置指令中的第8位至第9位取值为第五值时,第四时延可以配置为第四时延值;当配置指令中的第8位至第9位取值为第六值时,第四时延可以配置为第七时延值。

[0090]

图5是本公开一示例性实施例中的配置指令中的第2位至第9位的组成示意图。如图5所示,第2位至第9位[1:8]中的第2位和第3位[1:2]可以是内存行地址传输到列地址的延迟时间(time row address selet-to-colum address select delay,trcd)对应第一时延,第4位至第5位[3:4]可以是内存行地址预充电时间(row address selet precharge time,trp)对应第二时延;6位至第7位[5:6]可以是写恢复延时(wr for write recovery,twr)对应第三时延;第8位至第9位[7:8]可以是tccdl对应第四时延。tccdl可以是同一个bank中col to col的时间,在本公开中可以理解为写命令到下一个写命令,或者读命令到下一个读命令中间的间隔。

[0091]

在本公开一些可能的实施方式中,第一时延值可以是4tck,第二时延值可以是5tck,第三时延值可以是6tck,第四时延值可以是7tck,第五时延值可以是11tck,第六时延值可以是12tck,第七时延值可以是8tck,在第2位至第3位分别取值为第三值、第四值、第五值和第六值时,第一时延、第二时延、第三时延和第四时延对应的延时值参见表7。

[0092]

表7

[0093]

可以理解的是,对于存储器芯片ddr5,jedec的标准要求可以是trcd为17.5ns,twr为30ns,trp为17.5ns,tccdl为20ns。

[0094]

本公开实施例中,通过将配置指令中的第2位至第3位配置为第三值、第四值、第五值和第六值中的任一值,可以确定第一时延为对应的时延值(第一时延值、第二时延值、第三时延值和第四时延值中的一种);通过将配置指令中的第4位至第5位配置为第三值、第四值、第五值和第六值中的任一值,可以确定第二时延为对应的时延值(第一时延值、第二时延值、第三时延值和第四时延值中的一种);通过将配置指令中的第6位至第7位配置为第三值、第四值、第五值和第六值中的任一值,可以确定第三时延为对应的时延值(第三时延值、第四时延值、第五时延值和第六时延值中的一种);通过将配置指令中的第8位至第9位配置为第三值、第四值、第五值和第六值中的任一值,可以确定第四时延为对应的时延值(第一时延值、第二时延值、第四时延值和第七时延值中的一种)。

[0095]

在本公开的一些实施例中,在存储器芯片为16gb的ddr5的情况下,操作指令可以包括5位。其中:操作指令中的第1至第2位可以用于配置对存储器芯片进行测试时所采用的目标读写方式,当操作指令中的第1至第2位取值为第三值时,目标读写方式配置可以为列页优先读写方式;当操作指令中的第1至第2位取值为第四值时,目标读写方式配置可以为列优先读写方式;当操作指令中的第1至第2位取值为第五值时,目标读写方式配置可以为行优先读写方式;操作指令中的第3位可以用于配置对存储器芯片进行测试时所采用的目标读写操作,当操作指令中的第3位取值为第一值时,配置的目标读写操作可以为写操作,

当所述操作指令中的第3位取值为所第二值时,配置的目标读写操作可以为读操作;操作指令中的第4位和第5位可以用于配置对存储器芯片进行测试时所采用的目标地址寻址顺序,当操作指令中的第4位取值为第一值时,配置的目标地址寻址顺序可以为地址递增寻址顺序;当操作指令中的第4位取值为第二值时,配置的目标地址寻址顺序可以为地址递减寻址顺序;当操作指令中的第5位取值为第一值时,配置的目标地址寻址顺序可以为缺省寻址,当所述操作指令中的第5位取值为第二值时,配置的目标地址寻址顺序可以为跳跃寻址;目标写入数据、目标读写方式、目标地址寻址顺序和目标读写操作用于确定所述目标测试图形。

[0096]

图6是本公开一示例性实施例中的操作指令中的第1位至第5位的组成示意图。如图6所示,操作指令的第1至第3位[0:2]可以是cmd,其中,操作指令的第1位和第2位[0:1]对应读写方式配置位;操作指令的第3位[3]对应读写操作配置位;操作指令的第4位和第5位[3:4]可以是addr对应地址寻址顺序配置位。操作指令的第1位和第2位[0:1]在取值分别为第三值、第四值和第五值时的目标读写方式参见下表8。

[0097]

表8

[0098]

从表8中可以看出,本公开实施例中未用到操作指令的第1位和第2位[0:1]为11时的定义。

[0099]

操作指令的第3位[2]在取值分别为第一值和第二值时的目标读写操作可以参见下表9。

[0100]

表9

[0101]

其中,wr表示写操作,rd表示读操作。

[0102]

操作指令的第4位[3]在取值分别为第一值和第二值时的目标地址读写顺序可以参见下表10。

[0103]

其中,up可以对应地址递增寻址顺序;down可以对应地址递减寻址顺序。

[0104]

表10

[0105]

操作指令的第5位[4]在取值分别为第一值和第二值时的目标地址读写顺序可以参见下表11。

[0106]

表11

[0107]

其中,default可以对应缺省寻址;jump可以对应跳跃寻址。

[0108]

本公开实施例中,通过将操作指令中的第1至第2位配置为第三值、第四值和第五值中的任一值,可以确定目标读写方式为列页优先读写方式、列优先读写方式行优先读写方式中的对应读写方式;通过将操作指令中的第3位配置为第一值和第二值中的任一值,可

以确定目标读写操作为对应的读操作或写操作;通过将操作指令中的第4位和第5位分别配置为第一值或第二值,可以确定目标地址寻址顺序为地址递增寻址顺序、地址递减寻址顺序、缺省寻址和跳跃寻址中的对应寻址顺序,如此可以根据目标写入数据、目标读写方式、目标地址寻址顺序和目标读写操作确定目标测试图形,有利于mbist电路通过操作指令对存储器芯片进行不同测试图形的测试。

[0109]

本公开又一示例性实施例提供了一种存储器芯片测试方法。存储器芯片中可以包括mbist电路。本公开实施例提供的一种存储器芯片测试方法的步骤包括:步骤s11:mbist电路可以从测试设备接收配置指令。

[0110]

步骤s12:mbist电路可以根据配置指令配置对存储器芯片进行测试时的目标测试模式。

[0111]

步骤s13:mbist电路可以从测试设备接收操作指令。

[0112]

步骤s14:mbist电路可以根据操作指令控制对存储器芯片采用目标测试图形进行测试。

[0113]

本公开实施例中,通过mbist电路从测试设备接收配置指令,根据配置指令配置对存储器芯片进行测试时的目标测试模式,通过mbist电路从测试设备接收操作指令,根据操作指令确定对存储器芯片进行测试时的目标测试图形,以便于通过mbist电路在目标测试模式下采用目标测试图形对储器芯片进行测试,实现不同测试模式和不同目标测试图形下对存储器芯片的测试,测试覆盖范围全面,且在不同测试模式包括at speed模式时,可以进行at speed测试,同时通过复用mbist电路的方式,可以最大程度减少测试产生的面积开销,同时减少测试设备的使用时间,减少测试成本。

[0114]

本公开再一示例性实施例提供了一种存储器芯片测试方法。存储器芯片中可以包括存储器内建自测试mbist电路。本公开实施例提供的一种存储器芯片测试方法的步骤包括:步骤s21:mbist电路可以从测试设备接收内建自测试使能信号。

[0115]

步骤s22:mbist电路可以根据内建自测试使能信号触发开启针对存储器芯片的测试。

[0116]

步骤s23:mbist电路可以从测试设备接收配置指令。

[0117]

步骤s24:mbist电路可以根据配置指令配置对存储器芯片进行测试时的目标测试模式。

[0118]

步骤s25:mbist电路可以从测试设备接收操作指令。

[0119]

步骤s26:mbist电路可以根据操作指令控制对存储器芯片采用目标测试图形进行测试。

[0120]

本公开实施例中,通过mbist电路从测试设备接收内建自测试使能信号,并根据内建自测试使能信号触发开启针对存储器芯片的测试,有利于mbist电路根据接收的配置指令和操作指令对存储器芯片在目标测试模式和目标测试图形的配置下进行对应的测试。

[0121]

图7是本公开一示例性实施例中的mbist电路的组成结构示意图。

[0122]

如图7所示,本公开实施例中的mbist电路70可以包括:控制电路701和信号生成电路702。控制电路701可以用于接收并解析测试设备发送的配置指令和操作指令,根据解析结果生成控制信号。信号生成电路702可以用于接收并根据控制信号生成对存储器芯片进

行测试时的测试图形信号、测试指令信号、测试地址信号和测试时钟频率信号,以对存储器芯片进行测试。

[0123]

本公开的实施例中,通过控制电路接收并解析测试设备发送的配置指令和操作指令,根据解析结果生成控制信号,根据信号生成电路接收并根据控制信号生成对存储芯片进行测试时的测试图形信号、测试指令信号、测试地址信号和测试时钟频率信号,以实现对存储器芯片的测试。

[0124]

在本公开的一些实施方式中,控制信号可以包括目标时钟频率对应的时钟频率控制信号、目标操作时序对应的时序控制信号、目标写入数据对应的写入数据控制信号、目标读写方式对应的读写方式控制信号、目标地址寻址顺序对应的地址寻址顺序控制信号和目标读写操作对应的读写操作控制信号。目标时钟频率可以用于确定存储芯片的目标测试模式。

[0125]

参见图7所示,信号生成电路702可以包括时钟生成电路7021、指令生成电路7022、地址生成电路7023和数据生成电路7024。时钟生成电路7021可以用于根据时钟频率控制信号生成对存储器芯片进行测试时的测试时钟频率信号,指令生成电路7022可以用于根据操作时序控制信号、读写操作控制信号、读写方式控制信号生成对所述存储器芯片进行测试时的测试指令信号,地址生成电路7023可以用于根据地址寻址顺序控制信号生成对存储器芯片进行测试时的测试地址信号,数据生成电路7024可以用于根据写入数据控制信号生成对存储器芯片进行测试时的测试图形信号。

[0126]

在一种可能的实施方式中,在配置指令对应的信号为的情况下,目标时钟频率对应的信号可以是,目标操作时序对应的信号可以是,目标写入数据对应的信号可以是,目标压缩模式对应的信号可以是。在操作指令对应的信号为的情况下,目标读写方式对应的信号可以是,目标读写操作对应的信号可以是,目标地址寻址顺序对应的信号可以是。

[0127]

在本公开一些实施方式中,通过缓冲器对配置指令对应的信号进行缓冲,可以分别生成时钟频率控制信号、时序控制信号、写入数据控制信号和压缩模式控制信号。这里,缓冲器可以是串联的两个非门。

[0128]

读写方式控制控制信号,可以包括列页优先读写方式控制信号、列优先读写方式控制信号和行优先读写方式控制信号。读写方式控制控制信号可以是对目标读写方式对应的信号进行对应的逻辑运算生成的信号。

[0129]

读写操作控制信号也可以是通过缓冲器对目标读写操作对应的信号进行缓冲生成的。地址寻址控制信号可以包括通过缓冲器对目标地址寻址顺序对应的信号进行缓冲生成的地址递增递减寻址顺序控制信号和地址跳跃或缺省寻址顺序控制信号。

[0130]

图8是本公开一示例性实施例中的mbist控制电路的示意图。如图8所示,mbist控制电路701可以包括10个缓冲器801和逻辑电路802。

[0131]

通过10个缓冲器801分别将解析配置指令对应的信号得到的信号、、、、、和进行缓冲,对应得到时钟

频率控制信号clk_sel、延迟时间控制信号内存行地址预充电时间控制信号、写恢复延时控制信号、ccdl时间控制信号、写入数据控制信号和压缩模式控制信号,对解析操作指令对应的信号中的、和进行缓冲,得到读写操作控制信号wr、地址递增递减寻址顺序控制信号up down和地址跳跃或缺省寻址控制信号jump。缓冲器801可以包括串联的第一非门8011和第二非门8012。

[0132]

通过逻辑电路802分别将解析操作指令对应的信号中的得到的信号进行逻辑运算,得到列页优先读写方式(y page fast)控制信号ypagefast、列优先读写方式(y fast)控制信号yfast和行优先读写方式(x fast)控制信号xfast。这里,通过逻辑电路802可以包括第一或非门8021至第三或非门8023,第一或非门8021的第一输入端和第二输入端分别接收和,输出端输出列页优先读写方式(y page fast)控制信号ypagefast;第二或非门8022的第一输入端和第二输入端分别接收和第三非门8024输出端输出的的反相信号,输出端输出列优先读写方式(y fast)控制信号yfast;第三或非门8023的第一输入端和第二输入端分别接收第四非门8025的输出端输出的的反相信号和,输出端输出行优先读写方式(x fast)控制信号xfast。第三非门8024的输入端接收。第四非门8025的输入端的输入端接收。

[0133]

在本公开的一些实施方式中,根据时钟频率控制信号生成mbist电路对存储器芯片进行测试时的测试时钟频率信号,可以是根据时钟频率控制信号选择第一时钟频率值的时钟信号或第二时钟频率值的时钟信号作为对存储器芯片进行测试时的测试时钟频率信号。

[0134]

图9是本公开一示例性实施例的时钟生成电路的示意图。如图9所示,时钟生成电路clk_gen(对应时钟生成电路7021)可以包括第一二选一数据选择器910,第一二选一数据选择器910的第一输入端911和第二输入端912分别接收第二时钟频率值的时钟信号(tck1,例如当tck1等于2.5ns时,也可以表示为2.5ns_tck)和第一时钟频率值的时钟信号(tck2,例如当tck2等于5ns时,也可以表示为5ns_tck),第一二选一数据选择器910的控制端913用于接收时钟频率控制信号clk_sel,第一二选一数据选择器910的输出端914用于在时钟频率控制信号clk_sel的控制下,将第一时钟频率值的时钟信号或第二时钟频率值的时钟信号作为对存储器芯片进行测试时的测试时钟频率信号bist_clk输出。

[0135]

在本公开的一些实施方式中,根据操作时序控制信号、读写操作控制信号、读写方式控制信号生成对存储器芯片进行测试时的测试指令信号,可以是根据操作时序控制信号、读写操作控制信号、读写方式控制信号生成对存储器芯片进行测试时的测试指令信号分别对应选择对存储器芯片进行测试时的操作时序信号、读写操作信号和读写方式信号,形成对存储器芯片进行测试时的测试指令信号。

[0136]

图10是本公开一示例性实施例的指令生成电路的示意图。如图10所示,指令生成电路cmd_gen(对应指令生成电路7022)可以包括读写操作对应的指令生成电路w_r_cmd 1000、列页优先读写方式对应的指令生成电路ypagefast-cmd 1001、列优先读写方式对应的指令生成电路yfast_cmd 1002和行优先读写方式对应的指令生成电路xfast_cmd 1003。

[0137]

由于指令生成电路cmd_gen中的读写操作对应的指令生成电路w_r_cmd 1000与除

指令生成电路w_r_cmd 1000之外的其它指令生成电路的控制逻辑比较相似,因此,本公开实施例仅对读写操作对应的指令生成电路w_r_cmd 1000进行展示。

[0138]

读写操作对应的指令生成电路w_r_cmd 1000可以包括第二二选一数据选择器1004、第三二选一数据选择器1005、第四二选一数据选择器1006、第一与门1007、第二与门1008与第五非门1009。其中,第二二选一数据选择器1004的第一输入端和第二输入端分别连接延时值信号4ntck和5ntck,控制端1004

’’’

连接内存行地址传输到列地址的延迟时间控制信号;第三二选一数据选择器1005的第一输入端和第二输入端分别连接延时值信号6ntck和7ntck,控制端连接内存行地址传输到列地址的延迟时间控制信号;第二选一数据选择器1004的输出端和第三二选一数据选择器1005的输出端分别连接第四二选一数据选择器1006的第一输入端和第二输入端,第四二选一数据选择器1006的控制端连接内存行地址传输到列地址的延迟时间控制信号;读写操作控制信号w_r连接第五非门1009的输入端,第五非门1009的输出端与第四二选一数据选择器1006的输出端分别连接第一与门1007的第一输入端和第二输入端,第一与门1007的输出端输出对存储器芯片进行测试时的测试写信号bist_wr;第四二选一数据选择器1006的输出端(输出bist_w_r)与读写操作控制信号w_r分别连接第二与门1008的第一输入端和第二输入端,第二与门1008的输出端输出对存储器芯片进行测试时的测试读信号bist_rd。

[0139]

对应地,列页优先读写方式对应的指令生成电路ypagefast-cmd 1001可以生成对存储器芯片进行测试时的测试列页优先读写方式的测试读写方式信号bist_ypagefast、列优先读写方式对应的指令生成电路yfast_cmd 1002可以生成对存储器芯片进行测试时的测试列优先读写方式的测试读写方式信号bist_yfast和行优先读写方式对应的指令生成电路xfast_cmd 1003可以生成对存储器芯片进行测试时的测试行优先读写方式的测试读写方式信号bist_xfast。

[0140]

在本公开的一些实施例中,地址寻址顺序控制信号可以包括地址递增递减寻址顺序控制信号up_down和地址跳跃或缺省寻址顺序控制信号jump。根据地址寻址顺序控制信号生成对存储器芯片进行测试时的测试地址信号的实现方式,可以是生成第一行地址信号,根据地址跳跃或缺省寻址顺序控制信号jump从第一行地址信号和第二行地址信号选择目标行地址信号rowa《15∶0》,然后根据地址递增递减寻址顺序控制信号up_down选择目标行地址信号rowa《15∶0》或目标行地址信号的反相信号rowb《15∶0》作为对存储器芯片进行测试时的测试地址信号。

[0141]

图11是本公开一示例性实施例的地址生成电路的示意图。如图11所示,地址生成电路addr_gen(对应地址生成电路7023)可以包括地址计数器addr_cnt 1100、第五二选一数据选择器1101、第六二选一数据选择器1102和第六非门1103。

[0142]

其中,地址计数器addr_cnt 1100的输出端输出第一行地址信号;第五二选一数据选择器1101的第一输入端1101’和第二输入端分别接收第一行地址信号和第二行地址信号,第五二选一数据选择器1101的控制端接收地址跳跃或缺省寻址顺序控制信号jump,用于控制输出第一行地址信号或第二行地址信号作为目标行地址信号rowa《15∶0》,第五二选一数据选择器1101的输出端与第六非门1103的输入端连接,第六非门1103的输出

端与第五二选一数据选择器1101的输出端分别对应连接第六二选一数据选择器1102的第一输入端和第二输入端,第六二选一数据选择器1102的控制端接收地址递增递减寻址顺序控制信号up_down,用于选择目标行地址信号rowa《15∶0》或rowb《15∶0》信号作为对存储器芯片进行测试时的测试地址信号,通过输出端输出。

[0143]

在本公开的一些实施方式中,根据写入数据控制信号生成对存储器芯片进行测试时的测试图形信号,可以是根据写入数据控制信号从预设的多个写入数据中选择其中的一个作为对存储器芯片进行测试时的测试图像信号。

[0144]

这里,预设的多个写入数据可以包括全0的写入数据、01交替的写入数据、10交替的写入数据和全1的写入数据。

[0145]

图12是本公开一示例性实施例中的数据生成电路的示意图。如图12所示,该数据生成电路data_gen(对应数据生成电路7024)可以包括第七二选一数据选择器1201、第八二选一数据选择器1202和第九二选一数据选择器1203。

[0146]

其中,第七二选一数据选择器1201的第一输入端和第二输入端可以分别接收全0的写入数据、01交替的写入数据,第七二选一数据选择器1201的控制端可以接收写入数据控制信号,以选择全0的写入数据或01交替的写入数据输出;第八二选一数据选择器1202的第一输入端和第二输入单可以分别对应接收10交替的写入数据和全1的写入数据,第八二选一数据选择器的控制端可以接收写入数据控制信号,以选择10交替的写入数据或全1的写入数据输出;第七二选一数据选择器1201的输出端和第八二选一数据选择器1202的输出端分别对应连接第九二选一数据选择器1203的第一输入端和第二输入端,第九二选一数据选择器1203的控制端接收写入数据控制信号,以控制输出端选择输出第七二选一数据选择器1201的输出端输出的数据或第八二选一数据选择器1202的输出端输出的数据作为对存储器芯片进行测试时的测试图形信号data_in。

[0147]

本公开实施例中,通过时钟生成电路根据时钟频率控制信号生成对存储器芯片进行测试时的测试时钟频率信号,指令生成电路根据操作时序控制信号、读写操作控制信号、读写方式控制信号生成对存储器芯片进行测试时的测试指令信号,地址生成电路根据地址寻址顺序控制信号生成对存储器芯片进行测试时的测试地址信号,数据生成电路根据写入数据控制信号生成对存储器芯片进行测试时的测试图形信号。如此可以通过测试时钟频率信号、测试指令信号、测试地址信号和根据目标写入数据、目标读写方式、目标地址寻址顺序和目标读写操作确定的目标测试图形对存储器芯片进行相应的测试。

[0148]

在一些可能的实施方式中,控制信号还可以包括目标压缩模式对应的压缩模式控制信号,目标压缩模式与目标时钟频率对应,可以用于确定目标测试模式;压缩模式控制信号可以用于控制压缩模式电路根据压缩模式控制信号、测试指令信号和测试地址信号按照对应的压缩模式从存储器芯片中的存储阵列的相应存储单元读出数据,或者将测试图形信号写入至相应存储单元。

[0149]

在一种可能的实施方式中,压缩模式电路中可以包括比较电路,比较电路可以用于比较相应存储单元的读出数据和写入数据。

[0150]

在一种可能的实施方式中,在存储器芯片为ddr5的情况下,并行模式电路可以仅

包含32个banks的压缩模式对应的压缩电路,对于8bg的压缩模式则需要加入相应的电路。

[0151]

本公开实施例中,通过压缩模式控制信号可以控制压缩模式电路根据压缩模式控制信号、测试指令信号和测试地址信号按照对应的压缩模式从存储器芯片中的存储阵列的相应存储单元读出数据,或者将测试图形信号写入至相应存储单元,实现对存储器芯片的测试。

[0152]

图13是本公开一示例性实施例中的ate控制存储器芯片中mbsit电路进行测试的总体框图。如图13所示,存储器芯片的测试系统包括ate 131(对应测试设备)、mbist 132(对应mbist电路)、para模式模块133和存储阵列134(存储器控制芯片中的bank)。mbist电路132包括mbist控制器1321(对应mbist电路)、clk_gen 1322(对应时钟生成电路7021)、cmd_gen 1323(对应指令生成电路7022)、addr_gen 1324(对应地址生成电路7023)和data_gen 1325(对应数据生成电路7024)。

[0153]

其中,ate 131的输出端与mbist电路132的输入端耦接,用于向mbist电路下发mbist电路使能信号mbist_en(对应内建自测试使能信号),然后向mbist电路下发配置指令config_ctrl,通过配置指令调整运行时的时钟频率、操作时序和压缩模式,以进入不同的测试模式(测试环境),接着向mbist电路下发操作指令operation_ctrl完成不同的测试类型(pattern)。

[0154]

mbist 132的输出端与para模式模块133耦接,用于向para模式模块1331提供对存储器芯片进行测试时的测试指令信号cmd(对应包括图10中的测试写信号bist_wr和测试读信号bist_rd等)、对存储器芯片进行测试时的测试地址信号addr(对应图11中的测试地址信号)、对存储器芯片进行测试时的测试图形信号data_in(对应图12中的测试图形信号data_in)和存储器芯片进行测试时的测试压缩模式信号para_sel(对应图8中的压缩模式控制信号)。其中,para模式模块133包括比较电路1331,比较电路1331可以用于比较相应存储单元的读出数据和写入数据。

[0155]

mbist 132与存储阵列134连接,用于根据输入的对存储器芯片进行测试时的测试指令信号cmd、对存储器芯片进行测试时的测试地址信号addr、对存储器芯片进行测试时的测试图形信号data_in和存储器芯片进行测试时的测试压缩模式信号para_sel对存储阵列134进行对应测试模式和测试图形的测试。如此,可以进入不同的测试模式,并结合不同的读写方式及背景数据,实现多种故障类型的检测。

[0156]

本公开实施例中,通过bist控制电路解析配置指令,获得所配置的目标压缩模式,可以根据目标压缩模式确定目标测试模式;通过bist控制电路将目标压缩模式、测试指令信号和测试地址信号发送给并行模式电路,以通过并行模式电路确定从存储器芯片中的存储阵列的相应存储单元读出数据,或者将测试图形信号写入至相应存储单元,以对存储器芯片在目标测试模式、目标压缩模式下的测试,实现多种故障类型的测试。同时,通过比较电路比较相应存储单元的读出数据和写入数据,有利于根据比较结果及时发现测试问题。

[0157]

图14是本公开一示例性实施例的ate与mbist交互的具体电路图。如图14所示,参考图8至图13,和图13相比,图14不包括para模式模块133和存储阵列134部分的电路,ate 141对应图13中的ate 131,mbist控制器1421对应图13中的mbist控制器132和图8中的mbist控制电路701、clk_gen 1422对应图13中的clk_gen 1322和图9,data_gen 1423对应图13中的data_gen 1325和图12;cmd_gen 1424对应图13中的data_gen 1323和图10;addr_

gen 1425对应图13中的addr_gen 1324和图11。

[0158]

本公开的上述实施例提出的存储器芯片测试方法,可以通过测试设备来执行,该测试设备可以包括控制器和检测电路,其中,控制器可以是单片机、微控制单元(microcontroller unit,mcu)、数字信号处理器(digital signal processor,dsp)、现场可编程门在阵列(field-programmable gate array,fpga)、复杂可编程逻辑器件(complex programmable logic device,cpld)等控制单元,这里不进行具体限定。

[0159]

图15是本公开一示例性实施例的一种测试设备的组成结构示意图。如图15所示,该公开实施例的一种测试设备150可以包括:发送单元1501,可以用于向mbist电路发送配置指令,以配置存储器芯片进入的目标测试模式,存储器芯片中包括mbist电路;发送单元1501,还可以用于向mbist电路发送操作指令,以配置存储器芯片采用目标测试图形进行测试。

[0160]

在本公开的一些实施例中,发送单元1501还可以用于向mbist电路发送内建自测试使能信号,以用于触发开启mbist电路针对存储器芯片的测试。

[0161]

在本公开的一些实施例中,配置指令中可以包括压缩模式配置位,压缩模式配置位可以用于设置对存储器芯片进行测试时采用的目标压缩模式;目标压缩模式可以用于确定目标测试模式。

[0162]

在本公开的一些实施例中,目标压缩模式可以为压缩模式、无压缩模式的一种。其中:当目标压缩模式为压缩模式时,目标时钟频率可以配置为第一时钟频率值;当目标压缩模式为无压缩模式时,目标时钟频率可以配置为第二时钟频率值。

[0163]

在本公开的一些实施例中,配置指令中还可以包括操作时序配置位,操作时序配置位可以用于设置对存储器芯片进行测试时的目标操作时序。

[0164]

在本公开的一些实施例中,配置指令中还可以包括写入数据配置位,写入数据配置位可以用于设置对存储器芯片进行测试时的目标写入数据。

[0165]

在本公开的一些实施例中,操作指令中可以包括读写方式配置位、地址寻址顺序配置位和读写操作配置位;读写方式配置位可以用于设置对存储器芯片进行测试时所采用的目标读写方式;地址寻址顺序配置位可以用于设置对存储器芯片进行测试时所采用的目标地址寻址顺序;读写操作配置位可以用于设置对存储器芯片进行测试时所采用的目标读写操作;目标写入数据、目标读写方式、目标地址寻址顺序和目标读写操作可以用于确定所述目标测试图形。

[0166]

在本公开的一些实施例中,目标读写方式可以包括列优先读写方式、列页优先读写方式和行优先读写方式中的一种;目标地址寻址顺序可以包括地址递增寻址顺序、地址递减寻址顺序、缺省寻址和跳跃寻址中的一种;目标读写操作可以为读操作和写操作中的一种。

[0167]

本公开的示例性实施方式中还提供了一种mbist电路。

[0168]

本公开实施例又提供了一种电子设备。该实施例的电子设备可以包括一个或多个处理器,存储器,可以配置为存储一个或多个程序,当一个或多个程序被一个或多个处理器执行时,使得电子设备实现上述实施例的存储器芯片测试方法。

[0169]

本公开的示例性实施方式还提供了一种计算机可读存储介质,可以实现为一种程序产品的形式,其包括程序代码,当程序产品在电子设备上运行时,程序代码用于使电子设

备执行本说明书上述“示例性方法”部分中描述的根据本公开各种示例性实施方式的步骤。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1